Feburary 2011

ADS Ptolemy Simulation

#### © Agilent Technologies, Inc. 2000-2011

5301 Stevens Creek Blvd., Santa Clara, CA 95052 USA

No part of this documentation may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### Acknowledgments

Mentor Graphics is a trademark of Mentor Graphics Corporation in the U.S. and other countries. Mentor products and processes are registered trademarks of Mentor Graphics Corporation. \* Calibre is a trademark of Mentor Graphics Corporation in the US and other countries. "Microsoft®, Windows®, MS Windows®, Windows NT®, Windows 2000® and Windows Internet Explorer® are U.S. registered trademarks of Microsoft Corporation. Pentium® is a U.S. registered trademark of Intel Corporation. PostScript® and Acrobat® are trademarks of Adobe Systems Incorporated. UNIX® is a registered trademark of the Open Group. Oracle and Java and registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners. SystemC® is a registered trademark of Open SystemC Initiative, Inc. in the United States and other countries and is used with permission. MATLAB® is a U.S. registered trademark of The Math Works, Inc.. HiSIM2 source code, and all copyrights, trade secrets or other intellectual property rights in and to the source code in its entirety, is owned by Hiroshima University and STARC. FLEXIm is a trademark of Globetrotter Software, Incorporated, Layout Boolean Engine by Klaas Holwerda, v1.7 http://www.xs4all.nl/~kholwerd/bool.html . FreeType Project, Copyright (c) 1996-1999 by David Turner, Robert Wilhelm, and Werner Lemberg. QuestAgent search engine (c) 2000-2002, JObjects. Motif is a trademark of the Open Software Foundation. Netscape is a trademark of Netscape Communications Corporation. Netscape Portable Runtime (NSPR), Copyright (c) 1998-2003 The Mozilla Organization. A copy of the Mozilla Public License is at http://www.mozilla.org/MPL/, FFTW, The Fastest Fourier Transform in the West, Copyright (c) 1997-1999 Massachusetts Institute of Technology. All rights reserved.

The following third-party libraries are used by the NlogN Momentum solver:

"This program includes Metis 4.0, Copyright © 1998, Regents of the University of Minnesota", <u>http://www.cs.umn.edu/~metis</u>, METIS was written by George Karypis (karypis@cs.umn.edu).

Intel@ Math Kernel Library, http://www.intel.com/software/products/mkl

SuperLU\_MT version 2.0 - Copyright © 2003, The Regents of the University of California, through Lawrence Berkeley National Laboratory (subject to receipt of any required approvals from U.S. Dept. of Energy). All rights reserved. SuperLU Disclaimer: THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

7-zip - 7-Zip Copyright: Copyright (C) 1999-2009 Igor Pavlov. Licenses for files are: 7z.dll: GNU LGPL + unRAR restriction, All other files: GNU LGPL. 7-zip License: This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA. unRAR copyright: The decompression engine for RAR archives was developed using source code of unRAR program.All copyrights to original unRAR code are owned by Alexander Roshal. unRAR License: The unRAR sources cannot be used to re-create the RAR compression algorithm, which is proprietary. Distribution of modified unRAR sources in separate form or as a part of other software is permitted, provided that it is clearly stated in the documentation and source comments that the code may not be used to develop a RAR (WinRAR) compatible archiver. 7-zip Availability: http://www.7-zip.org/

AMD Version 2.2 - AMD Notice: The AMD code was modified. Used by permission. AMD copyright: AMD Version 2.2, Copyright © 2007 by Timothy A. Davis, Patrick R. Amestoy, and Iain S. Duff. All Rights Reserved. AMD License: Your use or distribution of AMD or any modified version of AMD implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies. User documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission." Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. AMD Availability: http://www.cise.ufl.edu/research/sparse/amd

UMFPACK 5.0.2 - UMFPACK Notice: The UMFPACK code was modified. Used by permission. UMFPACK Copyright: UMFPACK Copyright © 1995-2006 by Timothy A. Davis, All Rights Reserved. UMFPACK License: Your use or distribution of UMFPACK or any modified version of UMFPACK implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies. User documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission." Permission to modify the code

Advanced Design System 2011.01 - ADS Ptolemy Simulation and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. UMFPACK Availability: <u>http://www.cise.ufl.edu/research/sparse/umfpack</u> UMFPACK (including versions 2.2.1 and earlier, in FORTRAN) is available at

<u>http://www.cise.ufl.edu/research/sparse</u>. MA38 is available in the Harwell Subroutine Library. This version of UMFPACK includes a modified form of COLAMD Version 2.0, originally released on Jan. 31, 2000, also available at

<u>http://www.cise.ufl.edu/research/sparse</u> . COLAMD V2.0 is also incorporated as a built-in function in MATLAB version 6.1, by The MathWorks, Inc. <u>http://www.mathworks.com</u> . COLAMD V1.0 appears as a column-preordering in SuperLU (SuperLU is available at <u>http://www.netlib.org</u> ). UMFPACK v4.0 is a built-in routine in MATLAB 6.5. UMFPACK v4.3 is a built-in routine in MATLAB 7.1.

Qt Version 4.6.3 - Qt Notice: The Qt code was modified. Used by permission. Qt copyright: Qt Version 4.6.3, Copyright (c) 2010 by Nokia Corporation. All Rights Reserved. Qt License: Your use or distribution of Qt or any modified version of Qt implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the

terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful,

but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies.User

documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission."

Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. Qt Availability: <u>http://www.qtsoftware.com/downloads</u> Patches Applied to Qt can be found in the installation at:

\$HPEESOF\_DIR/prod/licenses/thirdparty/qt/patches. You may also contact Brian Buchanan at Agilent Inc. at brian\_buchanan@agilent.com for more information.

The HiSIM\_HV source code, and all copyrights, trade secrets or other intellectual property rights in and to the source code, is owned by Hiroshima University and/or STARC.

**Errata** The ADS product may contain references to "HP" or "HPEESOF" such as in file names and directory names. The business entity formerly known as "HP EEsof" is now part of Agilent Technologies and is known as "Agilent EEsof". To avoid broken functionality and to maintain backward compatibility for our customers, we did not change all the names and labels that contain "HP" or "HPEESOF" references.

**Warranty** The material contained in this document is provided "as is", and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this documentation and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with

Advanced Design System 2011.01 - ADS Ptolemy Simulation these terms, the warranty terms in the separate agreement shall control.

**Technology Licenses** The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license. Portions of this product include the SystemC software licensed under Open Source terms, which are available for download at <a href="http://systemc.org/">http://systemc.org/</a>. This software is redistributed by Agilent. The Contributors of the SystemC software provide this software "as is" and offer no warranty of any kind, express or implied, including without limitation warranties or conditions or title and non-infringement, and implied warranties or conditions merchantability and fitness for a particular purpose. Contributors shall not be liable for any damages of any kind including without limitation direct, indirect, special, incidental and consequential damages, such as lost profits. Any provisions that differ from this disclaimer are offered by Agilent only.

**Restricted Rights Legend** U.S. Government Restricted Rights. Software and technical data rights granted to the federal government include only those rights customarily provided to end user customers. Agilent provides this customary commercial license in Software and technical data pursuant to FAR 12.211 (Technical Data) and 12.212 (Computer Software) and, for the Department of Defense, DFARS 252.227-7015 (Technical Data - Commercial Items) and DFARS 227.7202-3 (Rights in Commercial Computer Software or Computer Software Documentation).

| About ADS Ptolemy                                                        | 8        |

|--------------------------------------------------------------------------|----------|

| ADS Ptolemy and UC Berkeley Ptolemy                                      | 8        |

| Timed Synchronous Dataflow Simulator                                     | 8        |

| Terminology                                                              | 9        |

| ADS Ptolemy GoldenGate Models                                            | 17       |

| Creating ADS Ptolemy Designs for Use in GoldenGate                       | 17       |

| Creating a Verification Testbench                                        | 19       |

| Exporting ADS Ptolemy Designs for Use in GoldenGate                      | 20       |

| Creating a Results Display for ADS Ptolemy Designs Used in GoldenGate    |          |

| Importing ADS Ptolemy Design to Use in GoldenGate in Cadence Environment | 21       |

| Cosimulation with Analog-RF Systems                                      | 22       |

| Setting Up the Analog/RF Circuit Schematic                               |          |

| Setting Up the Signal Processing Schematic                               |          |

| Automatic Verification Modeling (Fast Cosimulation)                      | 24       |

| Clustering of Circuit Subnetworks                                        |          |

| Feedback Loops                                                           |          |

| Named Connections and Measurements in Circuit Designs                    |          |

| Circuit Envelope Specific Rules                                          |          |

| Transient Simulation Specific Rules                                      |          |

| Nested Simulation Approach                                               |          |

| Interface Issues                                                         |          |

| Troubleshooting Common Problems                                          |          |

| Cosimulation Example                                                     |          |

| Data Types, Controllers, Sinks, and Components                           |          |

| Representation of Data Types                                             |          |

| Automatic or Manual Data Type Conversion                                 |          |

| Controllers                                                              |          |

|                                                                          |          |

| Sources and Sinks Control the Simulation                                 |          |

|                                                                          | 49<br>51 |

| Integrator Example       Opening Example Workspace                       | 51       |

|                                                                          |          |

| Integrator Design                                                        |          |

| Selecting and Placing Components                                         |          |

| Starting Simulation                                                      |          |

| Interactive Controls and Displays for ADS Ptolemy Simulation             |          |

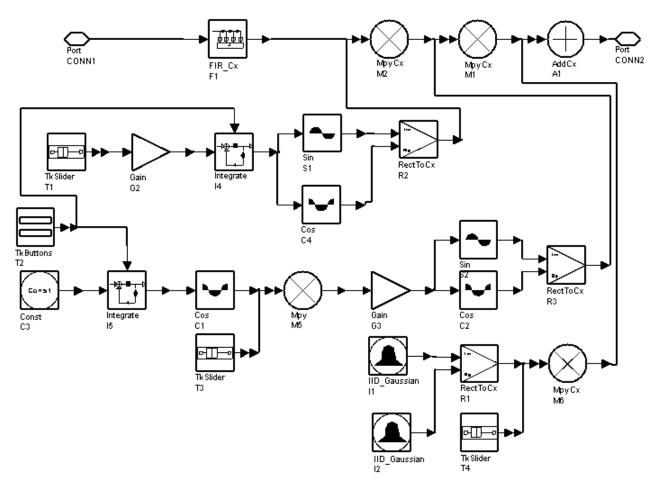

| TkSlider and TkPlot Components                                           | 57       |

| TkText and TkShowValues Components                                       | 59       |

| TkXYPlot Component                                                       | 60       |

| TkBarGraph Component                                                     | 61       |

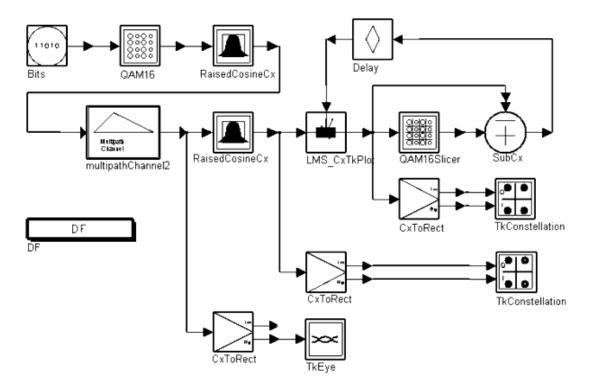

| LMS Adaptive Filter Components                                           | 62       |

| TkButtons Component                                                      | 63       |

| TkBreakPt Component'                                                     | 64       |

| TkMeter Component                                                        | 64       |

| TkShowBooleans Component                                                 | 64       |

| TkBasebandEquivChannel Component                                         | 65       |

| TclScript Component                                                      | 66       |

| TkEye, TkConstellation, TkHistogram, TklQrms, and TkPower Components     | 66       |

| References                                                               | 66       |

| MATLAB Cosimulation                                                      | 67       |

| Supported MATLAB Versions                                                | 67       |

| Setting Up MATLAB Cosimulation                                           | 67       |

| Simulating with MATLAB                                                   | 68       |

| Writing Functions for MATLAB Models                                      | 69       |

| Hiding MATLAB Code                                                       | 70       |

| Examples                                                                 | 70       |

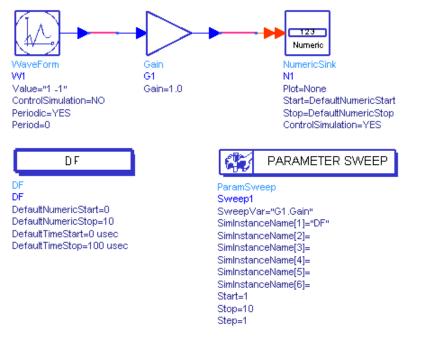

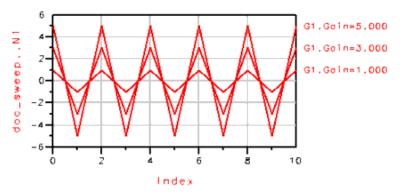

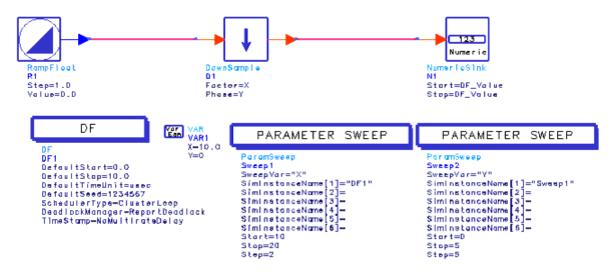

| Performing Parameter Sweeps                              |

|----------------------------------------------------------|

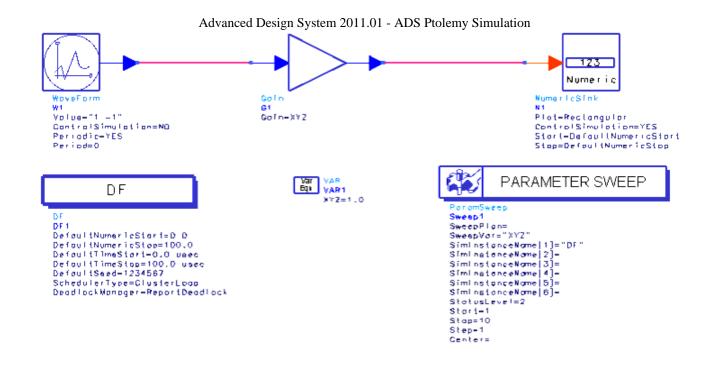

| Simple Parameter Sweeps                                  |

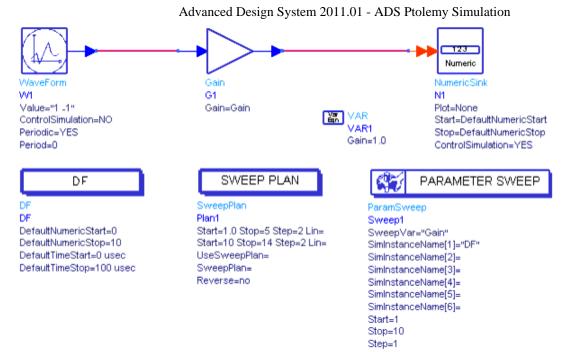

| Parameter Sweeps with Defined Variables 74               |

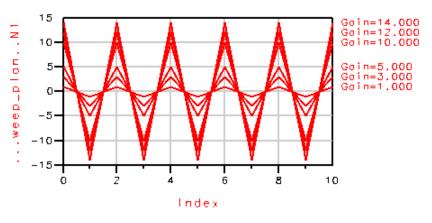

| Multiple Parameter Sweeps       75                       |

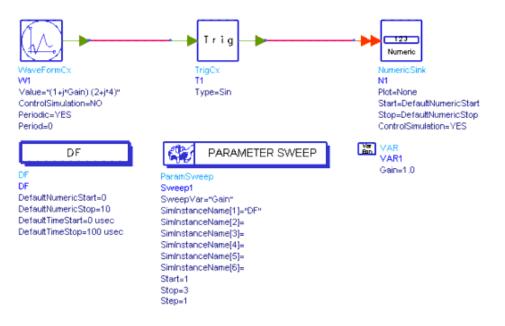

| String Type Parameter Sweeps                             |

| Multidimensional Parameter Sweeps       79               |

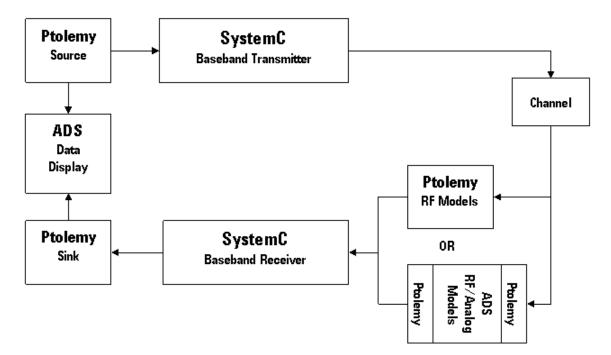

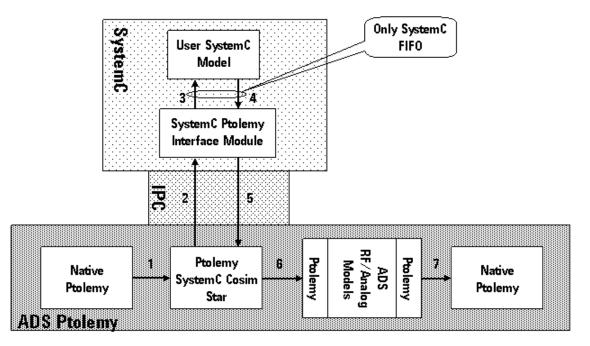

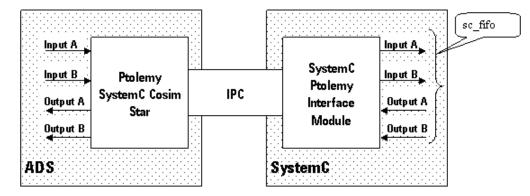

| SystemC Cosimulation                                     |

| Overview                                                 |

| SystemC Cosimulation Capabilities                        |

| Theory of Operation                                      |

| Importing a SystemC Model                                |

| Simulating Your Design                                   |

| Default SystemC Cosimulation Component Parameters        |

| Debugging SystemC Code                                   |

| Theory of Operation for ADS Ptolemy Simulation           |

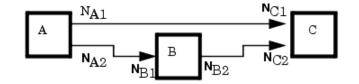

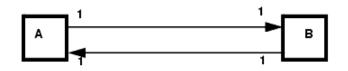

| Synchronous Dataflow                                     |

| Timed Synchronous Dataflow                               |

| References                                               |

| Understanding File Formats                               |

| Real Array Data                                          |

| Complex Array Data                                       |

| String Array Data                                        |

| Real Matrix Data                                         |

|                                                          |

| Fixed-Point Matrix Data                                  |

| Integer Matrix Data                                      |

| Complex Matrix Data                                      |

| SPW (.ascsig and .sig) File Formats 109                  |

| Time-Domain Waveform Data (.tim) File, MDIF ASCII Format |

| Agilent Standard Data Format (.dat) Files 113            |

| Understanding Parameters                                 |

| Value Types                                              |

| Parameter Editing                                        |

| Parameter Expressions                                    |

| Complex-Valued Parameters                                |

| Parameters for Fixed-Point Components                    |

| String Parameters                                        |

| Filename Parameters                                      |

| Array Parameters                                         |

| Reading Array Parameter Values From Files                |

| Parameters With Optimization and Swept Attributes        |

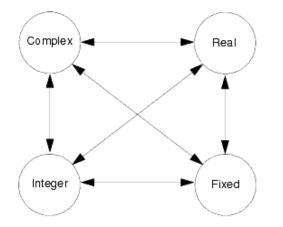

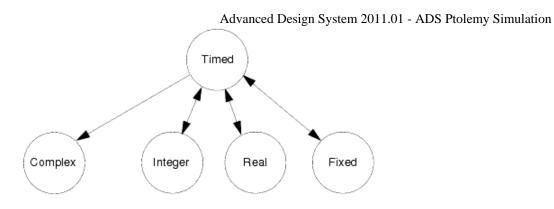

| Using Data Types                                         |

| Representation of Data Types 127                         |

| Data Types Defined                                       |

| Conversion of Data Types                                 |

| Using Nominal Optimization                               |

| Optimizing Various Parameter Types                       |

| Wireless Test Bench Designs                              |

| Creating a Wireless Test Bench Design                    |

| Using a WTB Design in ADS                                |

|                                                          |

| Creating a Results Display for WTB Designs 141           |

# **About ADS Ptolemy**

The ADS Ptolemy software provides the simulation tools you need to evaluate and design modern communication systems products. Today's designs call for implementing DSP algorithms in an increasing number of portions in the total communications system path, from baseband processing to adaptive equalizers and phase-locked loops in the RF chain. Cosimulation with ADS RF and analog simulators can be performed from the same schematic.

Using the ADS Ptolemy simulator you can:

- Find the best design topology using state-of-the-art technology with more than 500 behavioral DSP and communication systems models

- · Cosimulate with RF and analog simulators

- Integrate intellectual property from previous designs

- Reduce the time-to-market for your products

And, ADS Ptolemy features:

- Timed synchronous dataflow simulation

- Easy-to-use interface for adding and sharing custom models

- Interface to test instruments

- · Data display with post-processing capability

# **ADS Ptolemy and UC Berkeley Ptolemy**

The Ptolemy signal processing simulator has its roots at the University of California at Berkeley. UC Berkeley Ptolemy is a third-generation software environment that began in January of 1990. It is an outgrowth of two previous generations of design environments, Blosim and Gabriel, that were aimed at digital signal processing. Both environments use dataflow semantics with block-diagram syntax for the description of algorithms.

Built on the UC Berkeley Ptolemy code, ADS Ptolemy software includes a large number of behavioral, time-domain antenna and propagation models that are critical to communication systems designers. For DSP designers, fixed-point analysis is scalable up to 256 bits. The intuitive ADS user interface includes post-processing capability, cosimulation with analog/RF simulators, links to test instruments, online help, and a host of other features.

In Ptolemy, different specialized design environments are called *domains*. ADS Ptolemy has modified the proven synchronous dataflow domain to include timed components; this is called the *timed synchronous dataflow* domain.

# **Timed Synchronous Dataflow Simulator**

The timed synchronous dataflow domain captures years of Agilent EEsof expertise in system-level analog/RF simulation, while adding the benefits of dataflow technology. This domain enables fast RF simulation, integration with signal processing simulation, and cosimulation with Agilent EEsof circuit simulators. For more information on the timed synchronous dataflow simulator and the synchronous dataflow domain, refer to *Theory of*

# Terminology

Throughout most of the ADS Ptolemy documentation, we use the ADS terminology, which is standard EDA terminology. However, UC Berkeley Ptolemy has its own terminology and for users familiar with this terminology, or those who are writing their own models, the following table compares the terms. The UC Berkeley Ptolemy terminology is used only in *Theory of Operation for ADS Ptolemy Simulation* (ptolemy) and in the topics on building signal processing models found in the *User-Defined Models* (modbuild) documentation.

#### **Terminology Comparison**

| ADS Ptolemy Term     | UC Berkeley Ptolemy Term |

|----------------------|--------------------------|

| Component            | Star                     |

| Network (or circuit) | Galaxy                   |

| Top-level System     | Universe                 |

| Controller           | Target                   |

| Wire                 | Arc                      |

| Data (or signals)    | Particles (or tokens)    |

#### **\$HPEESOF\_DIR**

In UNIX installations, the environment variable specifying the directory in which the ADS software is installed. In Windows installations, the syntax, when needed, is %HPEESOF\_DIR%.

#### actor

An atomic (indivisible) function in a dataflow model of computation. An actor is called a component in ADS Ptolemy and a star in UCB Ptolemy.

#### arc

A wire that connects the output of one star or component with the input of another.

#### base class

A C++ object used to define common interfaces and common code for a set of derived classes. An object may be a base class and a derived class simultaneously.

System modeling consisting of functional specification plus modeling of the timing of an implementation (compare to functional modeling).

#### **Block**

The base class defined in the kernel for stars, galaxies, universes, and targets.

#### block

A star or a galaxy.

#### compile-time scheduling

A scheduling policy in which the order of block execution is pre-computed when the execution is started. The execution of the blocks thus involves only sequencing through this pre-computed order one or more times (compare to run-time scheduling).

#### derived class

A C++ object derived from some base class. It inherits all of the members and methods of the base class.

#### dataflow

A model of computation in which actors process streams of tokens. Each actor has one or more firing rules. Actors that are enabled by a firing rule may fire in any order.

#### domain

A specific implementation of a computation model.

#### Domain

The base class in the ADS Ptolemy kernel from which all domains are derived.

#### drag

The action of holding a mouse button while moving the mouse.

#### FFT

The Fast Fourier Transform (FFT) is an efficient way to implement the discrete Fourier transform in digital hardware.

#### firing

A unit invocation of an actor in a dataflow model of computation.

#### firing rule

A rule that specifies how many tokens are required on each input of a dataflow actor for that actor to be enabled for firing.

#### fork star

A star that reads one input particle and replicates it on any number of outputs.

#### functional modeling

System modeling that specifies input/output behavior without specifying timing (compare to behavioral modeling).

#### galaxy

A block that contains a network of other blocks.

#### **Gantt chart**

A graphical display of a parallel schedule of tasks. In ADS Ptolemy, the tasks are the firings of stars and galaxies.

#### homogeneous synchronous dataflow

A particular case of the synchronous dataflow model of computation, where actors produce and consume exactly one token on each input and output.

#### hpeesoflang

- A schema language used to define stars in ADS Ptolemy.

- The program that translates stars written in the hpeesoflang language to C++. In UCB Ptolemy, the equivalent language is called ptlang.

#### iteration

A set of executions of blocks that constitutes one pass through the pre-computed order of a compile-time schedule.

#### kernel

The set of classes defined in the ADS Ptolemy kernel.

#### layer

In the Schematic, a color with a given precedence. Colors with higher precedence will obscure colors with lower precedence.

#### member

A C++ object that forms a portion of another object.

#### method

A function defined to be part of an object in C++.

#### model of computation

A set of semantic rules defining the behavior of a network of blocks.

#### net

A graphical connection between ports in the schematic.

#### object

A data type in C++ consisting of members and methods. These members and methods may be private, protected, or public. If they are private, they can only be accessed by methods defined in the object. If they are protected, they can also be accessed by methods in derived classes. If they are public, they can be accessed by any C++ code.

#### palette

A schematic area that contains a library of block icons.

#### parameter

The initial value of a state.

#### particle

Data (for example, a floating-point value) communicated between blocks.

#### port

A star or galaxy input or output.

#### PortHole

The base class in the ADS Ptolemy kernel for all ports.

#### **Ptolemy**

A design environment that supports simultaneous mixtures of different computation models. Ptolemy, named after the second-century Greek astronomer, mathematician, and geographer, was developed at the University of California at Berkeley.

#### real time

The actual time (compare to simulated time).

#### RTL

Register-transfer level description of digital systems.

#### run-time scheduling

A scheduling policy in which the order of block execution is determined *on-the-fly*, as they are executed (compare to compile-time scheduling).

#### Scheduler

An object associated with a domain that determines the order of block execution within the domain. Domains may have multiple schedulers.

#### schematic

A block diagram.

#### SDF

A simulation domain using the synchronous dataflow model of computation.

#### simulated time

In a simulation domain, the real number representing time in the simulated system (compare to real time).

#### simulation

The execution of a system specification (an ADS Ptolemy block diagram) from within the ADS Ptolemy process (that is, execution without generating code and spawning a new process to execute that code).

#### simulation domain

A domain that supports simulation, but not code generation.

#### star

A component in ADS Ptolemy. An atomic (indivisible) unit of computation in an ADS

Advanced Design System 2011.01 - ADS Ptolemy Simulation Ptolemy application. Every ADS Ptolemy simulation ultimately consists of executing the methods of the stars used to define the simulation.

#### Star

The base class in the ADS Ptolemy kernel for all stars.

#### state

A member of a block that stores data values from one invocation of the block to the next.

#### State

The base class in the ADS Ptolemy kernel for all states.

#### stop time

Within a timed domain, the time at which a simulation halts.

#### symbol

A graphical object that represents a single block.

#### synchronous dataflow

A dataflow model of computation where the firing rules are particularly simple. Every input of every actor requires a fixed, pre-specified number of tokens for the actor to fire. Moreover, when the actor fires, a fixed, pre-specified number of tokens is produced on each output. This model of computation is particularly well-suited to compile-time scheduling.

#### target

An object that manages the execution of a simulation or code generation process. In ADS Ptolemy this is called a controller. For example, in code generation, the target would be responsible for compiling the generated code and spawning the process to execute that code.

The base class in the kernel for all targets.

#### Tcl

Tool command language-a textual, interpreted language developed by John Ousterhout at UC Berkeley. Tcl is embedded in ADS Ptolemy.

#### timestamp

A real number associated with a particle in timed domains that indicates the point in simulated time at which the particle is valid.

#### timed domain

A domain that models the evolution of a system in time.

#### Tk

A Windows and X-Windows toolkit for Tcl. The interactive sliders, buttons, and plotting capabilities of ADS Ptolemy are implemented in Tcl/Tk.

#### token

A unit of data in a dataflow model of computation. Tokens are implemented as particles in ADS Ptolemy.

#### universe

An entire ADS Ptolemy design.

#### VHDL

The VHSIC hardware description language, a standardized language for specifying hardware designs at multiple levels of abstraction.

#### wormhole

# **ADS Ptolemy GoldenGate Models**

Using ADS Ptolemy, a system designer can create a DSP system design that is available to an Analog/RF designer as a source or a measurement model (Sink) in Agilent Technologies GoldenGate Simulator in Cadence Analog Design Environment. This mechanism enables a system designer to make complex signal generation and system measurements available to an Analog/RF designer. The Analog/RF designer can then validate and verify the Analog/RF design or device under test (DUT) using the GoldenGate Simulator.

This topic describes how to create and export ADS Ptolemy designs to GoldenGate.

# **Creating ADS Ptolemy Designs for Use in GoldenGate**

The design must be created in a DSP Schematic window using only DSP components. A/RF cosimulation sub-circuits cannot be embedded inside the design. Any resistor(s) adjacent to the input or output port will have no impact on the Analog/RF DUT.

Currently, we only support exporting ADS Ptolemy source designs with all output ports and ADS Ptolemy sink designs with all input ports, separately.

#### ADS Ptolemy source design requirements for use in GoldenGate

- The ADS Ptolemy source design must not contain a DF controller.

- The ADS Ptolemy source design must not contain a sink type DSP component.

- The ADS Ptolemy source design must contain only output ports.

- The ARF\_Export component (available under Circuit Cosimulation palette) must be used to specify additional port information for GoldenGate.

- The "ComponentType" parameter in ARF\_Export must be set to "SOURCE"

- At most, one "*RF*" port is allowed in a source design to be exported to GoldenGate.

- The "*RFPortNum*" parameter in ARF\_Export must be set to the RF port number if there is one or zero if there is no RF port in the schematic.

- The design should generate timed baseband and/or RF signal appropriate for stimulating the Analog/RF DUT.

- In the presence of an "*RF*" port, the top level source design must contain "*FCarrier*" and "*ROut*" as design parameters.

- The design parameters could be set using "*File->Design Parameters*" from the schematic window. These design parameters will be available to be modified in Cadence schematic capture.

- The frequency of signal at "*RF*" type port must always be equal to "*FCarrier*" defined as a design parameter. Please be careful if Analog/RF designer is expected to modify this parameter in Cadence environment while using GoldenGate simulator.

- Make sure the "*Not Edited*" and "*Not Netlisted*" are NOT checked for "*FCarrier*" and " *ROut*" design parameters.

- The source signal, in GoldenGate, from "*RF*" port will be at "*FCarrier*" Hz and will have "*ROut*" ohms output resistance.

- The top level design to be exported must contain a VAR block containing a variable named "*MaxTimeStep*", representing time step at the output port(s).

- The value of time step in GoldenGate simulator, set by Analog/RF designer, must be smaller than the "*MaxTimeStep*" when using the exported source.

#### ADS Ptolemy sink design requirements for use in GoldenGate

- The ADS Ptolemy sink design must contain only input ports.

- The ARF\_Export component (available under Circuit Cosimulation palette) must be

used to specify additional port information for GoldenGate.

- The "*ComponentType*" parameter in ARF\_Export must be set to "*SINK*"

- At most, one "*RF*" port is allowed in a sink design to be exported to GoldenGate.

- The "*RFPortNum*" parameter in ARF\_Export must be set to the RF port number if there is one or zero if there is no RF port in the schematic.

- The design should read timed baseband and/or RF signal from Analog/RF DUT.

- In the presence of an "*RF*" port, the top level sink design must contain " *FMeasurement*" as design parameter.

- The design parameters could be set using "*File->Design Parameters*" from the schematic window. These design parameters will be available to be modified in Cadence schematic capture.

- The frequency of signal at "*RF*" type port will be equal to "*FMeasurement*" defined as a design parameter. Please be careful if Analog/RF designer is expected to modify this parameter in Cadence environment while using GoldenGate simulator.

- Make sure the "*Not Edited*" and "*Not Netlisted*" are NOT checked for "*FMeasurement*" design parameter.

- All ports in sink will exhibit infinite input resistance in GoldenGate. The output voltage at sink input in GoldenGate will depend on load resistance in GoldenGate Device Under Test (DUT).

- The top level design to be exported must contain a VAR block containing variable named "*MaxTimeStep*".

- The time step at all the input port(s) will be be adjusted to "*MaxTimeStep*" value automatically.

- The value of time step in GoldenGate simulator, set by Analog/RF designer, must be smaller than the "*MaxTimeStep*" when using the exported sink.

- The top level design to be exported must contain a VAR block containing variable named "*MinStopTime*", representing stop time for this sink. Th Stop time in GoldenGate simulator, set by Analog/RF designer, must be larger than the MinStopTime.

Each design can have parameters as required. These parameters will be available for modification in the Cadence environment while using the GoldenGate simulator. Parameters can be added using the *File > Design Parameters* in an ADS Schematic window.

# Features Not Supported in ADS Ptolemy Design for Use in GoldenGate

The ADS Ptolemy Design to be exported must not contain any of the following at any level of design hierarchy

- Any Analog/RF sub-design as component.

- Any SystemC Cosim component.

- Any HDL Cosim component.

- Any Matlab Cosim component.

- Any Interactive Controls and Displays component.

- Any Instruments component.

- Any component that is reading a file, where file location is NOT specified using an absolute path.

# **Creating a Verification Testbench**

Create a new top-level design and place the instances of the source and sink designs in it. Connect the source to the sink and add a DF controller. This top-level design must

# **Exporting ADS Ptolemy Designs for Use in GoldenGate**

In ADS 2011 ARF\_ExportPort has been removed and its functionality has been replaced with the new ARF\_Export controller. The automatic migration process in ADS will remove the instances of ARF\_ExportPort from GoldenGate source or sink deigns and insert the ARF\_Export controller. However, there is a known issue with the RFPortNum parameter. In some designs with baseband ports the parameter may be set incorrectly. The user will need to set the RFPortNum parameter to the RF port number, or to zero if there are only baseband ports in the design. If the parameter does not match the actual RF port number, the GoldenGate simulation will fail with an error "FCarrier specified is not similar to the carrier frequency of RF signal in Ptolemy," because GoldenGate treats baseband and RF ports differently.

#### **Export GoldenGate Virtual Testbench**

You can export either the whole verification testbench as a Virtual Testbench or the source or sink as a Virtual Testbench component. Select *Tools > Export ADS Ptolemy Design > As GoldenGate VTB* in the schematic window containing the design. You will be prompted for the location of the output files, and an *Export Status/Error/Warning* dialog box will appear showing the export progress.

A successful export process generates the files *<Design name>.vtb*, and *<Design name>\_ GG.net*.

#### **Export GoldenGate Model**

To export the CDF file, save the source or sink design and select *Tools > Export ADS Ptolemy Design > As GoldenGate model* in the schematic window containing the design (you will need to push into the source or sink from the verification testbench). An *Export Status/Error/Warning* dialog box appears showing the exporting progress. A temporary design window will open where the design will be instantiated before the export starts.

A successful export process generates the files *<Design name>\_GG.cdf*, and *<Design name>\_GG.net*. These files are saved with the exported design under the workspace directory *...\_wrk/adsptolemy/GoldenGate*.

# **Creating a Results Display for ADS Ptolemy Designs Used in GoldenGate**

An ADS Ptolemy design may have complex data that an Analog/RF designer will not know how to interpret. To help simplify data analysis, the System designer must use the following steps:

- 1. System designer must perform verification of the design as mentioned earlier to create a dataset in ADS.

- 2. Open a new DDS window. Add one or more new pages and name them appropriately.

- 3. Add correct equations/plots/configurations on the new pages.

- 4. Save this DDS file as a template by choosing *File > Save as Template* on the DDS window. Select the *User* category to save the template.

- 5. The template file is saved under *\$HOME/hpeesof/circuit/templates*.

- 6. Copy the template file to ...\_*wrk/adsptolemy/templates*.

- 7. Place an OutputOption controller in the designs schematic window. (The OutputOption component can be placed at any level of hierarchy in the design.)

- 8. Add the data display template name, created above, to the list of names. More than one data display template is allowed for a given design.

- 9. Re-export the design.

When this design is used in a GoldenGate simulation, the templates listed in the OutputOption controller will be inserted in the DDS window. The users can launch DDS via *Results > Start ADS DDS Display ...* menu item in ADE. Please consult GoldenGate documentation for further details about invoking Data Display inside GoldenGate-ADE.

# **Importing ADS Ptolemy Design to Use in GoldenGate in Cadence Environment**

If you exported a Virtual Test Bench, you can use *Setup > Virtual Test Bench...* in *Analog Environment* to set it up.

The ADS Ptolemy Designs exported as CDF files can be imported using *Tools* > *Import* ADS Ptolemy Models into GoldenGate....

Please consult GoldenGate documentation for further details about import process and how to simulate these models.

# **Cosimulation with Analog-RF Systems**

Simulation of behavioral DSP designs along with analog/RF circuit designs is critical to the success of the integrated components, devices, and subsystems used in today's wireless applications. The need to verify the impact of real-world analog/RF issues on the DSP algorithms and vice versa in a tightly integrated environment is highly desirable.

For designs of low complexity, it is possible to use separate simulators for the signal processing and analog/RF portions and then integrate the results. However, today's state-of-the-art designs using a mix of analog/RF and dedicated on-chip DSP blocks require high levels of integration at the two-environment boundary. Advanced Design System cosimulation between signal processing and circuits addresses this need. ADS Ptolemy provides the signal processing simulation, while the analog/RF simulation is provided by either the Circuit Envelope or High-Frequency SPICE (Transient) simulators.

Other types of cosimulation include placing MATLAB components or HDL blocks in a signal processing simulation. This topic describes cosimulation with analog/RF systems.

#### 0 Note

For information on A/RF cosimulation with Cadence refer to the *Cadence Library Integration* (dynlnklc) documentation. For specific details, see *Running a DSP and Analog - RF Cosimulation with RFIC Dynamic Link* (dynlnkug).

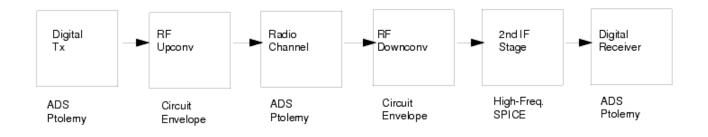

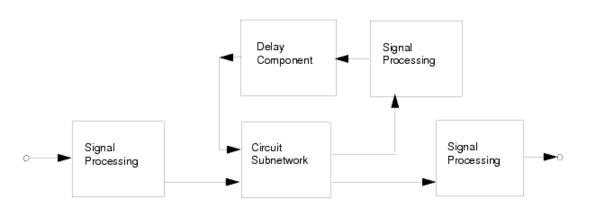

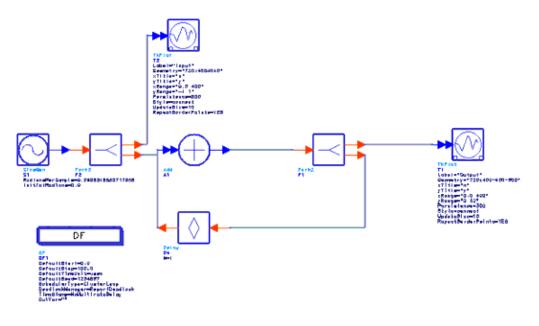

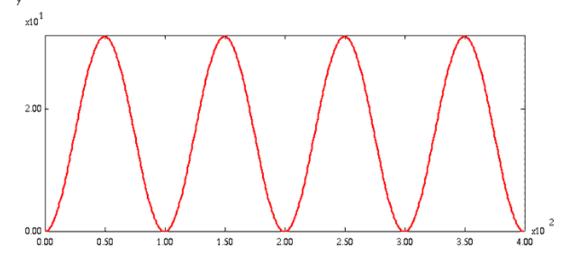

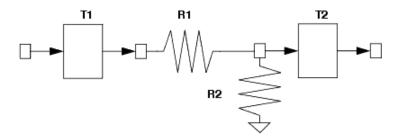

The following figure shows a mixture of RF circuitry and DSP components. ADS provides a variety of analog/RF circuit simulators, including Linear, Harmonic Balance, Circuit Envelope, High-Frequency SPICE, and Convolution.

#### 🖯 Note

Circuit Envelope and High-Frequency SPICE simulators are included with some, not all, ADS suites.

For signal processing simulation, ADS Ptolemy is used. Only circuits simulated with either Circuit Envelope or High-Frequency SPICE can be instantiated as a subnetwork and included in a signal processing schematic. These circuit blocks can then be simulated along with signal processing components. The steps needed for cosimulation are described in the next section.

Cosimulation: Different Design Portions Simulated by Different Simulators in the Same Schematic

# Setting Up the Analog/RF Circuit Schematic

Advanced Design System 2011.01 - ADS Ptolemy Simulation

| 1   |           |   |     |     |                  |                 | _  |     |   |   |   |       |     |   |   |   |   |   |   |   |        |    |    |   |   |   |   |     |       |     |                  |               |            |           |     |           |   |     |

|-----|-----------|---|-----|-----|------------------|-----------------|----|-----|---|---|---|-------|-----|---|---|---|---|---|---|---|--------|----|----|---|---|---|---|-----|-------|-----|------------------|---------------|------------|-----------|-----|-----------|---|-----|

| 1   |           |   | Isp | u t |                  | Inpu            |    |     |   |   | R | ee ti | Jul |   |   |   |   |   |   | R | • \$30 | ut |    |   |   |   |   | 186 | g t O | ut  |                  |               | Reo        | tout      | £   | $\sim$    |   | r . |

|     | or t<br>1 | 5 | *   | 2   |                  |                 |    | DIO |   |   | ŀ |       | 5   |   |   | · |   |   |   |   | 0-0    | .5 | pF |   |   |   | 4 | ۶ĥ  | -19   | 6   | ·                | •             | 4          |           |     | ort.<br>2 |   | ŀ   |

| . 1 | lum=1     | , |     | L   |                  | +               |    | ,   |   |   | , |       | ,   | - |   | , |   |   | 1 | ᅕ |        | ,  |    |   | - |   |   | ₹.  | ,     |     | ,                | -             | ,          | ,         | . N | lum-2     | l | -   |

|     |           | - | -   |     | DLode.<br>DIODER |                 | Ι. | -   |   |   |   |       |     | - | - |   |   |   |   |   |        |    |    |   |   | - |   | ٢.  |       |     |                  | -             | -          |           |     |           |   |     |

|     |           | - | -   |     | 1s= .<br>Rs=     |                 | -  | -   |   |   |   |       | -   | - |   |   | · |   |   | ŧ | -      |    |    |   |   | - |   | 1   |       |     |                  | -             | -          | -         |     |           |   | -   |

|     |           | - | -   | ·   | N= .<br>Tt=      | ikf=<br>Nbv=    |    | -   | · | · |   | Ŀ.    |     | - |   | · | · |   |   |   |        |    | ·  | · | ŀ | - | 4 |     |       | ·   | ·                | -             | -          |           |     |           |   |     |

|     |           |   |     |     | Cio= .           | I by I<br>Nby I |    |     |   |   |   |       |     | - |   |   |   |   |   |   |        |    |    |   |   |   |   |     |       | Ċ,  |                  |               |            |           |     |           |   | ۱.  |

|     | ,         | - | -   | ,   | Ha .             | There           |    | -   |   |   | , | ,     | -   | - |   | , |   |   | , | - |        |    | Ŧ  |   |   | - | - | ,   |       | L   |                  | ΕN            | ٧ŧ         | E.L.(     | DР  | Έ         |   |     |

|     |           | - | -   |     | Inter x=         |                 | -  | -   |   |   |   |       | -   | - | - |   |   |   |   | - |        |    | 7  |   |   | - |   |     |       |     |                  | a Cop         | e.         |           | ÷   |           |   |     |

|     |           | - | -   |     | Kt= .            |                 | -  | -   |   |   |   |       | -   | - | - |   |   |   |   | - |        |    |    |   | - | - | - |     |       |     | En v:<br>Vicí x: | 2<br>Dride    | r≌S        | -         |     |           |   |     |

|     |           | - |     |     | Fe= .<br>By=     |                 | Ŀ  | 4   |   |   |   |       | Ŀ   |   |   |   |   | ÷ |   |   | 4      |    |    |   |   |   | 4 |     |       | - 8 | Fre<br>Drd       |               | -11<br>]≌5 | MHZ       | :   |           |   | ·   |

|     | ,         | ~ | ,   | ,   | lbv= .           | ,               | ,  |     | , | , | , | ,     | 7   |   | , | , | , | , | , |   | ,      | ,  | ,  | , | , |   |   |     |       | 1   | Fun<br>Dvie      | d0ve<br>rsiom | isa<br>pie | [1]=      |     |           | , | ,   |

|     |           | - | -   |     |                  |                 | -  | -   |   |   |   |       |     | - |   |   |   |   | - | - |        |    |    |   |   | - |   | -   |       |     | Sto<br>Sfej      | 9=2<br>≓D.    | U#4<br>D1  | c<br>ušec | e.  |           |   |     |

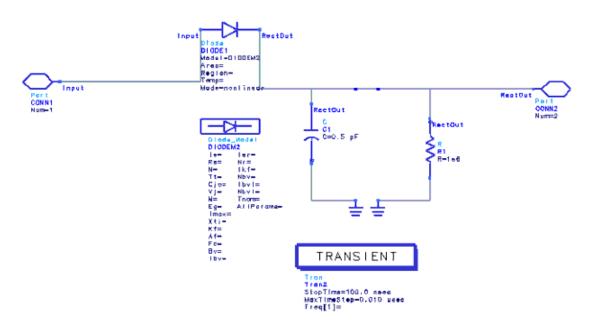

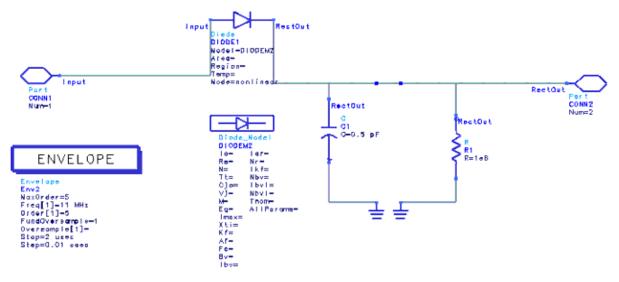

**Diode Rectifier Circuit Design Used in Cosimulation**

To create circuit designs for cosimulation.

- 1. In the analog/RF circuit Schematic window, create a circuit schematic that includes a simulation component for either Circuit Envelope (called ENV) or High-Frequency SPICE simulation (called TRAN).

- 2. Generally, use Circuit Envelope for an RF simulation and High-Frequency SPICE (transient) for a baseband simulation.

- 3. Do not use Envelope and Transient simulators in the same design; if you want to keep both controllers in a design use activate/deactivate.

- 4. Add ports to your design.

- 5. Save your design.

In the previous figure, a diode rectifier is set to be simulated with the Circuit Envelope simulator. Next, we will place this subnetwork in the signal processing schematic where it will be represented as a block.

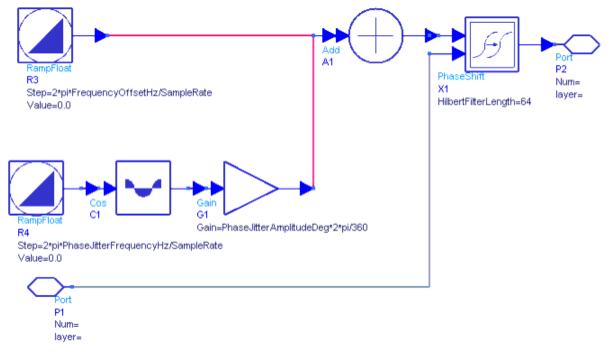

# **Setting Up the Signal Processing Schematic**

|                                                                     | Circuit Design (Diode<br>Rectifier)   | EnvOutSelector Component Used with Circuit<br>Envelope Cosimulation   |  |  |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|                                                                     |                                       |                                                                       |  |  |  |  |  |  |  |  |  |  |  |

|                                                                     |                                       |                                                                       |  |  |  |  |  |  |  |  |  |  |  |

|                                                                     | ENV .                                 |                                                                       |  |  |  |  |  |  |  |  |  |  |  |

|                                                                     |                                       |                                                                       |  |  |  |  |  |  |  |  |  |  |  |

| Pf<br>Jisightw1.0-1*2.0. Titop=.01 uses.<br>Vidth=10 FCorrier=1 Mit | O1<br>Outraq=All.                     | Te<br>Lete = "Env Butputt".                                           |  |  |  |  |  |  |  |  |  |  |  |

| Pariode32                                                           |                                       | xTliator                                                              |  |  |  |  |  |  |  |  |  |  |  |

| · · · · · · · <mark>· · <u>· · · ·</u> · · · · ·</mark>             |                                       | yTitle="y"<br>                                                        |  |  |  |  |  |  |  |  |  |  |  |

|                                                                     |                                       | Persistence=150                                                       |  |  |  |  |  |  |  |  |  |  |  |

| · · · · · · · · · <b>· · · · · · · · · · </b>                       | · · · · · · · · · · · · · · · · · · · | ApdateSfree10                                                         |  |  |  |  |  |  |  |  |  |  |  |

| an an an an an an an an <mark>a sta an</mark> an an an an           |                                       | . DF                                                                  |  |  |  |  |  |  |  |  |  |  |  |

| a a a a a a <u>Tipleta a a</u> a a a a                              |                                       | <u></u>                                                               |  |  |  |  |  |  |  |  |  |  |  |

| Lobel="Complex Bits"<br>Second ry="720x400+0+0+0                    |                                       | 11314r1-0.0                                                           |  |  |  |  |  |  |  |  |  |  |  |

| · · · · · · · · · · · · · · · · · · ·                               | Terbu                                 | tTideUnit=heat                                                        |  |  |  |  |  |  |  |  |  |  |  |

| yPanga-"0.0 100.0 *                                                 | albd                                  | itBeed=1234687<br>aier7905—CiusterLoop<br>achterage="Tages theodiec.k |  |  |  |  |  |  |  |  |  |  |  |

| Stylemoscone I                                                      |                                       | tomp=Hailul t1rot=Deloy                                               |  |  |  |  |  |  |  |  |  |  |  |

| RepeatBerderPointe-VEB                                              |                                       |                                                                       |  |  |  |  |  |  |  |  |  |  |  |

|                                                                     |                                       |                                                                       |  |  |  |  |  |  |  |  |  |  |  |

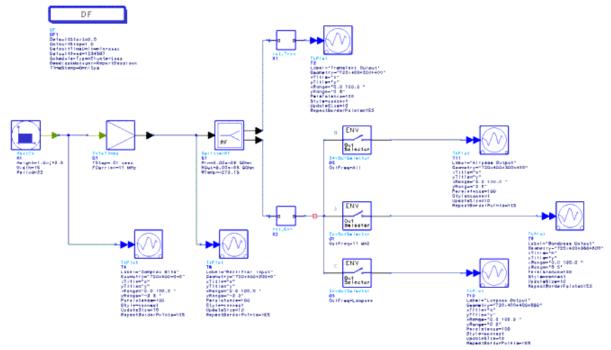

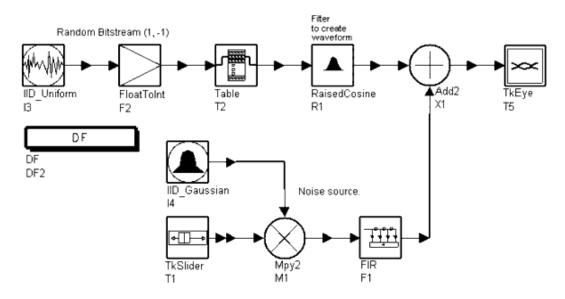

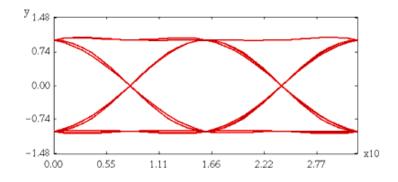

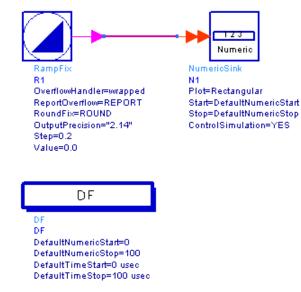

Signal Processing Design Using Circuit Shown in Previous Figure

Advanced Design System 2011.01 - ADS Ptolemy Simulation To create signal processing designs for cosimulation:

- 1. Choose the circuit design you want and place it in your signal processing schematic.

- 2. Add the signal processing components.

- 3. Add the signal processing controller(s).

- 4. Connect the circuit design to the signal processing components.

- 5. For cosimulation with the Circuit Envelope simulator, see <u>Circuit Simulation</u> <u>Controllers</u>.

- 6. If your circuit subnetworks have feedback loops between them, see Feedback Loops.

- 7. If the input signal into the circuit subnetwork is not of type Timed, see <u>Numeric-to-</u><u>Timed Converters</u>.

- 8. Select the initialization method of the circuit inputs in the Signal Processing DF controller; see *DF* (*Data Flow*) *Controller* (ptolemy).

- 9. Start the simulation.

#### **Circuit Simulation Controllers**

As stated earlier, ADS Ptolemy can cosimulate with only the Circuit Envelope or High-Frequency SPICE simulators. Any circuit simulation control components other than ENV or TRAN (such as for harmonic balance or S-parameter simulation) are ignored in the cosimulation from the signal processing schematic.

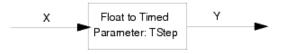

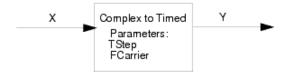

#### **Numeric-to-Timed Converters**

Both Circuit Envelope and Transient simulators deal with time-domain signals. Therefore, signal processing components connected to the circuit subnetwork must be the *timed* type. If the input component (connecting signal processing components to the circuit) produces numeric data, place an appropriate numeric-to-timed converter (such as float-to-timed or complex-to-timed) in your schematic. These components (located in the Signal Converters library) ensure that the input into the circuit subnetwork is in the time domain. Refer to <u>Time Converters</u> for more information.

# Automatic Verification Modeling (Fast Cosimulation)

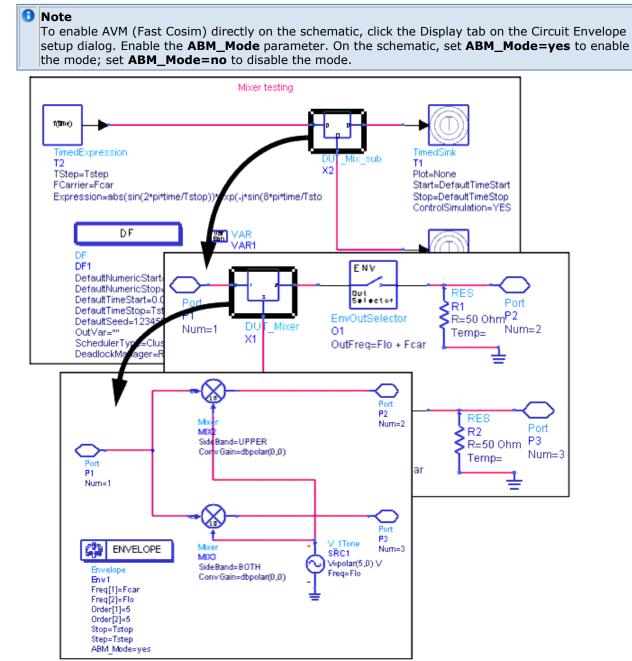

Automatic Verification Modeling is a simulation mode that can significantly accelerate formerly lengthy cosimulations of Analog/RF circuits. You can enable Automatic Verification Modeling in the Circuit Envelope Simulation Controller. When enabled, this mode characterizes an analog subcircuit into a behavior model, then the model is used to predict the response of the subcircuit at each time point. For details about Automatic Verification Modeling, see *Automatic Verification Modeling* (cktsimenv).

The following steps demonstrate how to enable the fast cosimulation mode using *PtolemyDocExamples/AVM\_wrk* from the examples directory:

- 1. Select *AVM\_wrk* from the *PtolemyDocExamples* directory.

- 2. Open the design *TestMixer*.

- 3. In the Schematic window, select DUT\_Mix\_sub, and push into its hierarchy, then push into the DUT\_Mixer hierarchy as shown in the following figure.

- 4. In the DUT\_Mixer, double-click the Envelope simulation controller to open its setup

dialog. Select the Cosim tab, and click **Enable AVM (Fast Cosim)** to enable the mode.

Pushing into TestMixer Hierarchy to Enable AVM (Fast Cosim)

# **Clustering of Circuit Subnetworks**

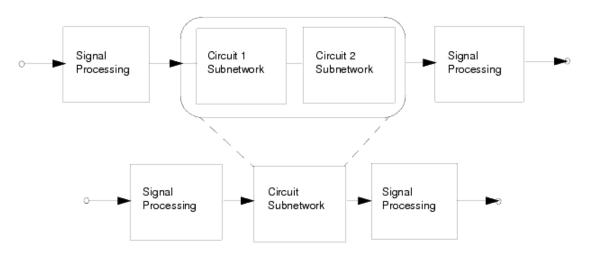

Clustering is the process of defining the boundaries of the signal processing and analog/RF simulators. Initially, this boundary is defined by circuit schematics, where you define the circuit subnetworks and then make an instance of those on the Signal Processing schematic. However, there is a bit more to clustering than what is on the two schematics.

Circuit subnetworks directly connected in the Signal Processing schematic are automatically clustered and treated as one circuit subnetwork, as shown in the following

figure. Therefore, use only one circuit simulation control component in either of the two (or more) directly connected subnetworks.

**Connected Subnetworks Treated as One**

#### **Connected Circuit Subnetworks**

When two circuit subnetworks defined on two different circuit schematics are connected on a Signal Processing schematic, the two circuit subnetworks are clustered into one (this is done transparently and should not concern the user). However, if each of these two circuit subnetworks use their own simulation controller, then the circuit engine would not know which one to choose for simulation and would result in an error message.

#### **Connected Resistors**

Another aspect of clustering is when circuit components available on the Signal Processing schematic (resistors in the first release of Advanced Design System) are connected to a circuit subnetwork. In this case, such resistors will be absorbed into the circuit subnetwork during the clustering and will be simulated by the circuit engine as part of circuit subnetwork.

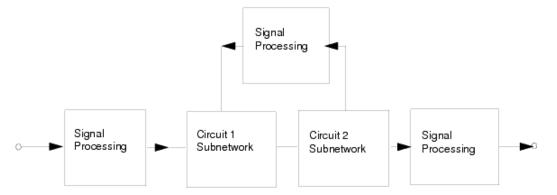

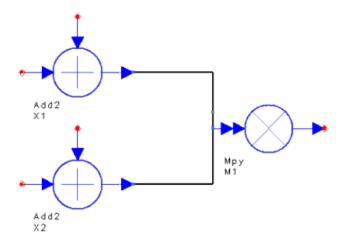

### **Feedback Loops**

Circuit subnetworks that form a feedback loop via signal processing components require a delay component in the feedback loop to facilitate the signal processing simulation scheduling, as shown in the following two figures. If such a delay is not present, an error message will be issued. To have the program automatically insert the delay, you must edit the DF (data flow) controller parameters. To do this, double-click the controller, choose the *Options* tab, then select *Resolve deadlock by inserting tokens* from the DeadlockManager drop-down list. For more information about deadlocks, refer to *Deadlocks* (ptolemy).

Advanced Design System 2011.01 - ADS Ptolemy Simulation

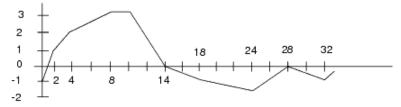

Feedback Loop Before Delay Added by Program

Feedback Loop After Delay Added by Program (Delay Not Shown on Schematic)

# Named Connections and Measurements in Circuit Designs

Named connections and measurements included in the circuit schematic design (such as for a voltage) are ignored in cosimulation. The only results you get from a cosimulation are obtained from the Signal Processing schematic using Sink components or Interactive Components and Displays items.

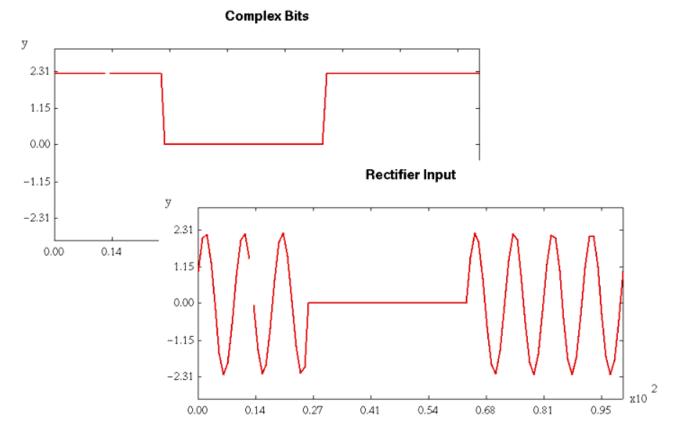

# **Circuit Envelope Specific Rules**

The output of the Circuit Envelope simulator is a collection of time waveforms, each at a different fundamental frequency. You must select the waveform you want by specifying this fundamental frequency. You do this by choosing the *EnvOutSelector* or *EnvOutShort* component from the Circuit Cosimulation library. Refer to <u>EnvOutSelector and</u> <u>EnvOutShort Components</u> for more information. Place this component at all circuit subnetwork output ports in the Signal Processing schematic.

Circuit Envelope simulation requires that many parameters be set up in the circuit schematic. For more information, refer to Advanced Design System's *Circuit Envelope*

Advanced Design System 2011.01 - ADS Ptolemy Simulation Simulation documentation. For cosimulation, the key parameter is the *Step* parameter. This is the time step used by the simulator, and can be set equal to or less than the time step at the connecting port in the signal processing schematic design. Other important parameters for cosimulation (especially nonlinear designs) are *MaxOrder*, *Freq*[], and *Order*[]. Make sure that the *OutFreq* parameter specified at the *EnvOutSelector* or *EnvOutShort* component is among the fundamental frequency or harmonics specified by the Circuit Envelope controller.

To enable or disable the addition of noise from the Circuit Envelope components, use the *Turn on all noise* parameter in the Env Params tab. For cosimulation, the *Nonlinear* noise button, the *Small-signal* button, and their corresponding tab pages should not be used as they are not used during cosimulation. Note that explicit noise sources, such as \_V\_Noise\_, are always on. The *Turn on all noise* enables or disables only the noise generated by non-source models, such as the resistors, lossy transmission lines, and transistors.

The amplitude of these noise sources is determined by the Circuit Envelope bandwidth, which is determined by 1/(Time Step). Normally, this Circuit Envelope timestep would be the same timestep as that used by Ptolemy, so the total noise bandwidths are the same. However, for designs where the Ptolemy waveform is changing too rapidly for the analog simulation and the user has reduced the Circuit Envelope timestep, then the Circuit Envelope noise bandwidth also increases. Depending on the circuit behavior, this broader bandwidth noise may appear at the circuit output, where it is now effectively sampled by the EnvOut element. This sampling will then alias all the higher bandwidth. If this is not the desired simulation behavior, then a filter may need to be placed at the circuit output. Of course, this will also filter any signals being passed back to the Ptolemy simulation.

# **Transient Simulation Specific Rules**

When cosimulation with ADS Ptolemy and the Transient simulator is required, the circuit schematic must have a Transient (Tran) simulation controller (a *transient simulation component*). No explicit user setting is required for the Tran controller; that is, the default parameters will work for cosimulation. However, the Tran controller's Freq [x] parameter is required when there are any frequency-dependent sources. The Freq [x] parameter specifies the fundamental frequency.

There is a difference between ADS Ptolemy and the Transient simulator regarding how they treat signals at time=0- (before t=0) that may cause unexpected results; they have different simulation assumptions for time=0-. ADS Ptolemy assumes signal states at time=0- are zeros, while the Transient simulator assumes signal states at time=0- the same as time=0. For a circuit with a given input signal stimulus to give the same response for both Ptolemy/Transient cosimulation and for Transient simulation alone, the circuit signal stimulus for the Ptolemy/Transient cosimulation must have a zero value at time=0. If the signal stimulus into the circuit during a Ptolemy/Transient cosimulation is not zero at time=0, then the cosimulated Transient simulator will result in output signals that are not expected when compared to a Transient-alone simulation. To force the circuit input to be zero during a Ptolemy/Transient cosimulation, the workaround is to change the CktCosimInputs setting on the Options tab of the DF (data flow) controller (refer to *Options Tab* (ptolemy) for details).

# **Nested Simulation Approach**

ADS cosimulation is based on a nested simulation approach. In this use model, you first create your circuit designs on the circuit schematic. This circuit design can be tested using appropriate circuit sources and measurements with either the Circuit Envelope or High-Frequency SPICE simulators. Once the circuit design has been verified, ports to be interfaced with the signal processing design are identified and placed. Next, you place an instance of the design on the Signal Processing schematic and connect it to the other blocks. The combined schematic design can now be simulated.

#### **Signal Processing Model of the Circuit Network**

ADS Ptolemy uses a data flow simulation approach, and this simulation is controlled using the DF (data flow) controller component. To understand this section, you need to be aware that this simulation is based on invoking a *schedule*. A schedule tells the simulator engine to *fire* components in a certain order and with a certain frequency. A simulation is typically a repetition of a schedule many times.

From the data flow engine perspective, a circuit subnetwork on the Signal Processing schematic is just a component with a certain number of input and output ports. This circuit subnetwork is part of the schedule determined by the data flow engine. It would be fired just like any other component according to the schedule, and as many times as required. Every time the circuit subnetwork is fired, the circuit simulator (designated by the simulation controller on the circuit schematic) continues to carry on the simulation based on the input it receives from the signal processing interface. Once the circuit simulator completes its analysis, it passes the simulation results back to the signal processing interface. This cycle repeats as many times as the scheduler requires. The duration of the circuit simulation each time it is invoked is determined by the time step provided by the connecting signal processing component at the input interface to the circuit subnetwork.

#### **Circuit Model of the Signal Processing Network**

From the circuit simulator engine point of view, the circuit that is cosimulated with the signal processing design is the clustered circuit subnetwork (see Clustering of Circuit Subnetworks) inclusive of any resistor (RES) component associated with signal processing components at the inputs or outputs of the circuit. Thus the circuit is interfaced to signal processing components that appear as ideal sources at the circuit inputs (with 0 ohm source resistance) and as ideal loads at the circuit outputs (with infinite ohm load resistance). The circuit output can interface directly to signal processing components at the circuit outputs for circuit transient cosimulation. However, for circuit envelope cosimulation, the circuit outputs must be connected to an envelope selector component (EnvOutSelector, EnvOutShort) which is then connected to signal processing components. The EnvOutSelector output provides an open circuit to any resistor associated with an attached signal processing component input. The EnvOutShort output provides connectivity to any resistor associated with an attached signal processing component input. Each circuit input may have only one zero ohm signal processing source connected. When multiple signal processing signals are desired at one circuit input, then each zero ohm source can have their signals combined with any suitable resistor combining network. Those source resistors are typically included in the definition of *Timed* signal processing

component outputs. The user must keep in mind that any resistor (RES) component associated with signal processing components at the inputs or outputs of the circuit are really part of the circuit and not part of the signal processing component.

### **Interface Issues**

At the interface boundary of the signal processing and analog/RF circuit simulators, there needs to be an exchange of information. The semantics and fundamentals of simulation in the two application areas are quite different and therefore, you need to understand these differences for proper use. The following sections outline the most important aspects of this interface.

#### **Time Step**

Time samples for signal processing are one fixed time step apart. However, both Envelope and Transient simulators define the time step in the simulation controller with various options.

The Transient Simulator controller component has several parameters, including Start time, Stop time, Min time step, and Max time step (see the Time Setup tab). In addition, the Integration tab contains a time step control method parameter with Fixed, Iteration Count, and Truncation Error options. For more information, refer to *Transient and Convolution Simulation* (cktsimtrans).

For cosimulation with the Transient simulator, keep in mind one key issue: The Transient simulator may need time steps smaller than ADS Ptolemy's Time Step to satisfy its own setup requirements. In addition, the Transient simulator, when needed, will take additional time steps to match the time points in the signal processing simulation. Only time steps that match the signal processing time points will be passed on to ADS Ptolemy.

#### 0 Note

For all practical purposes, the only parameter that may concern the cosimulation user is the Max time step. Other parameters in the Transient Simulation control component can remain at default values. For the Circuit Envelope simulator, the time step parameter in the ENV Simulation controller component should be set equal to or less than the Time Step at the signal-processing-to-circuit interface.

Depending on the Time Step value you set, the simulator will set the internal Circuit Envelope time step to either the Ptolemy time step value, or to an integer sub-multiple of this value. Time step values less than the Ptolemy time step value are sometimes required to achieve the desired accuracy, due to rapidly changing signals and the integration required for capacitive and inductive components. If the Circuit Envelope value is less than one-tenth of the Ptolemy time step value, a warning is generated to alert you to this so you can avoid inadvertent small time step values that might unnecessarily be slowing the cosimulation.

#### 🖯 Note

The Stop time for the simulation is determined by the Signal Processing Data Flow controller and/or Sinks. The Circuit Envelope Stop time does not affect the duration of the cosimulation. The Stop Time value is used in a few models and, ideally, should be set to reflect an approximate stop time range. As an example, for explicit Analog/RF Noise sources that have a user-specified baseband frequency response, this stop time value is used to determine the maximum duration of the pre-computed random noise sequence. Presently, the stop time is limited to about 2.1M (=2<sup>21</sup>) times the time step value. If the cosimulation runs longer than this, then this noise data is repeated.

#### **Delays in Feedback Loops**

As stated earlier, Data Flow simulation requires that a Delay component exist in the feedback loops for proper activation of the schedule. Circuit subnetworks that form a feedback loop, for this same reason require a delay component in their path. Typically, a DelayRF component in such feedback loops will suffice. If such a delay does not exist, ADS Ptolemy will report a deadlock by default.

#### **Time Converters**

The common signal being exchanged between signal processing Data Flow components and the circuit simulators (Circuit Envelope and Transient) is a time-domain signal. All three engines, hence, deal with the notion of time step.

The signal entering the circuit subnetwork should be Timed. The Transient simulator deals only with real-baseband time-domain signals while Circuit Envelope can handle both baseband and complex envelope timed signals.

If the signal entering into the circuit subnetwork is not Timed (that is, the signal is Numeric), you should place a FloatToTimed, FixToTimed, IntToTimed, or CxToTimed converter to accommodate the conversion. Although ADS Ptolemy will place appropriate converters when they do not exist, it is *always* a good practice to explicitly place and connect these converters in your design. This will ensure that the input parameters into the circuit subnetwork are correct, as well as helping to debug possible errors that may occur.

#### **Carrier Frequency**

In the case of cosimulation with the Circuit Envelope simulator, the timed signal entering the circuit subnetwork is typically a carrier-modulated timed signal. This means that timed data has an F  $_{\rm c}$  field that is passed to the Circuit Envelope simulator, which is needed by

the simulator. The Circuit Envelope simulator, depending on a particular design, will generate a number of time-domain waveforms, each associated with a carrier (harmonic) frequency. Since ADS Ptolemy supports only *one* carrier frequency at each node, you need to select which one of the waveforms you desire in the signal processing portion of the design. This is done by placing a Circuit-Envelope specific component described next.

#### **EnvOutSelector and EnvOutShort Components**

When cosimulating with the Circuit Envelope simulator, additional information is needed for proper cosimulation. This is done by connecting an EnvOutSelector or EnvOutShort component (from the Circuit Cosimulation library in the Signal Processing schematic) to each output port of the subnetwork design.

The EnvOutSelector component acts as an open, blocking everything connected to its output from loading the circuit. If such loading is desired, use the EnvOutShort

component. The EnvOutShort component acts as a short and therefore loads the circuit with the connecting Signal Processing components.

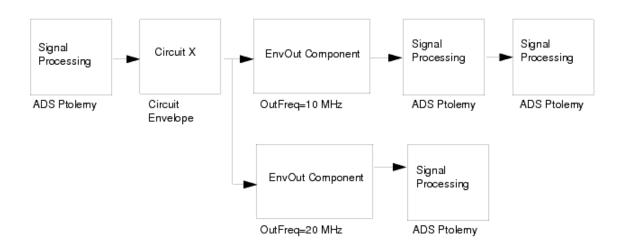

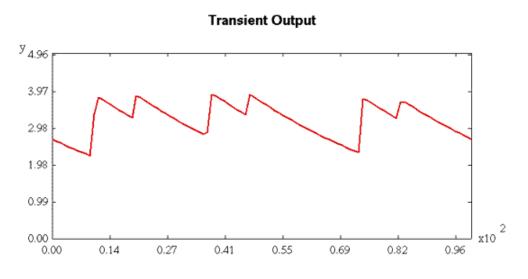

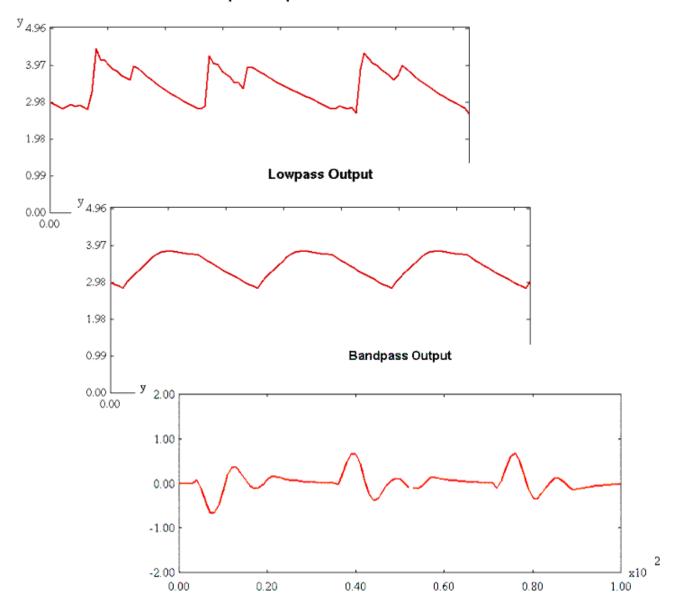

The EnvOutSelector and EnvOutShort components have a parameter called *OutFreq*. OutFreq specifies which waveform is selected from the time-domain waveforms at the output of the Circuit Envelope simulator. OutFreq has the following options:

- Lowpass-selects the time-varying DC component.

- Bandpass-(default) lets you specify any frequency.

- Allpass-forms the composite (baseband) signal.

One or more EnvOut components (EnvOutSelector and EnvOutShort) can be connected to each output port of a circuit subnetwork as illustrated in the following figure. All waveforms generated by the Circuit Envelope simulator can be accessed in a Signal Processing schematic.

*EnvOut* Components (*EnvOutSelector* or *EnvOutShort*) at each Circuit Subnetwork Output Port

When an EnvOutSelector or EnvOutShort component is used with a design simulated by the Transient simulator, their effect is an open or a short, respectively. Otherwise they do not affect transient cosimulation designs and can remain in place without any impact on the cosimulation.

#### **Snapping Rule**

In the Bandpass option of the OutFreq parameter, you can type in the desired fundamental whose time waveform you are interested in. If the frequency you specify does not exist in the list of fundamentals, the interface program will search and snap to the nearest fundamental. Anything within 0.01% of a fundamental will be snapped to that fundamental frequency. If the frequency specified in the Bandpass option of OutFreq is not within 0.01% of the fundamental, a default value of 100 MHz will be used and a warning message issued.

# **Troubleshooting Common Problems**

While the cosimulation use model is intuitive, the following information will help you avoid

- 1. Only the Transient and Circuit Envelope circuit simulators can cosimulate with ADS Ptolemy. Other circuit simulation controllers on the analog/RF schematic (such as Sparameter or AC) will be ignored in cosimulation.